Programmieren von EtherCAT-I/O mit FPGA Intelligence

Inhalt

- Notwendigkeit deterministischer verteilter I/O

- EtherCAT RIO – Slave-Chassis für EtherCAT

- Warum FPGA Intelligence hinzufügen?

- Unterschiede in der API für die LabVIEW FPGA-Programmierung

- Spezielle FPGA-Funktionen und Anwendungsfälle

- Zusammenfassung

Sie können Echtzeit-Verteilungssysteme mit EtherCAT-I/O entwickeln, die mit FPGAs (Field-Programmable Gate Arrays) programmierbar sind. Das modulare EtherCAT RIO-Slave-Chassis bietet intelligente Erweiterungs-I/O für NI CompactRIO und andere programmierbare Automatisierungscontroller (PACs), die EtherCAT unterstützen. Mit dem NI LabVIEW FPGA Module können Sie EtherCAT RIO-Slave-Chassis programmieren, wodurch Sie programmierbare verteilte Geräte für benutzerdefiniertes Timing, Closed-Loop-Steuerung und Inline-Verarbeitung erhalten.

Notwendigkeit deterministischer verteilter I/O

Der Bedarf an Erweiterungs-I/O ergibt sich häufig bei der Entwicklung eines Echtzeitsystems mit großer Kanalanzahl oder weitläufiger Stellfläche. Mit der Erweiterungs-I/O können Sie verteilte Messungen hinzufügen oder die ursprüngliche Anwendung erweitern. Der Aufbau einer eigenen Synchronisierungsarchitektur zur Aufrechterhaltung des Determinismus dieses Steuerungssystems kann jedoch schnell kompliziert und nicht skalierbar werden. Es gibt heute Echtzeit-Ethernet-I/O-Technologien wie EtherNet/IP, EtherCAT und PROFINET, die diese Anwendungen vereinfachen können. Daher sollten Sie ein Echtzeitnetzwerk aus Remote-I/O verwenden, das auf die deterministische Kommunikation mit dem Hauptcontroller ausgelegt ist.

EtherCAT RIO – Slave-Chassis für EtherCAT

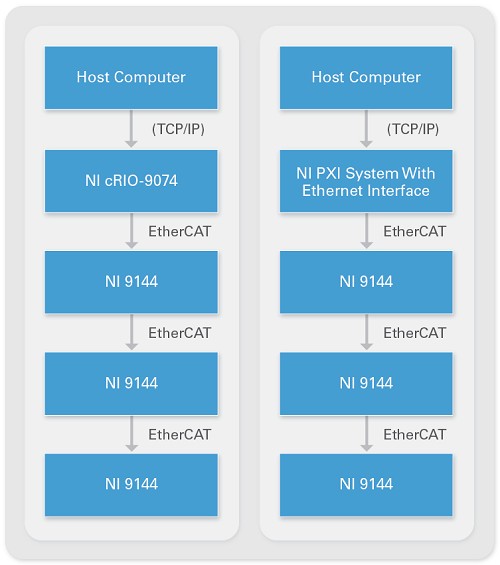

Das EtherCAT RIO-Erweiterungs-Chassis fügt Ihrem CompactRIO-, PXI- oder Industrie-Controller-System EtherCAT-I/O hinzu. Dieses robuste Chassis mit acht Steckplätzen für Module der C-Serie überträgt Daten deterministisch über ein offenes Echtzeit-Ethernet-Protokoll mit der Bezeichnung EtherCAT. Sie können Ihre zeitkritischen Anwendungen erweitern, indem Sie mehrere EtherCAT RIO-Erweiterungs-Chassis vom EtherCAT-Master-Controller aus in Reihe schalten. Die Softwarekonfiguration und LabVIEW-Programmiererfahrung sind so konzipiert, dass sie beim Hinzufügen von Echtzeit-EtherCAT-I/O einfach zu verwenden sind.

Abbildung 1: Typisches EtherCAT-System mit Master-Controllern und verteilten Slave-Geräten von NI

Warum FPGA Intelligence hinzufügen?

EtherCAT RIO-Slave-Chassis können sowohl mit LabVIEW Real-Time als auch mit LabVIEW FPGA Module programmiert werden. Die Programmierung im NI-Scan-Modus mit LabVIEW Real-Time bietet eine praktische, sofort einsatzbereite Erfahrung für einfache Erweiterungs-I/O. Der NI-Scan-Modus bietet Ihnen sofortigen Zugriff auf die physischen I/O-Werte auf den EtherCAT-RIO-Slave-Geräten durch einfaches Drag-and-Drop der I/O-Variablen sowie Live-Testpanels zur Überwachung der Systemleistung und zur erweiterten Fehlerbehebung. Warum also FPGA Intelligence zu Ihrer EtherCAT-Erweiterungs-I/O hinzufügen?

Die Programmierung des EtherCAT RIO-Slave-Chassis im FPGA-Modus öffnet Türen zu einem neuen Maß an Anpassung und Flexibilität für Ihre Anwendung. Durch die Integration von Entscheidungsfunktionen verkürzt sich die Reaktionszeit und es wird schnell und ohne Host-Interaktion auf die Umgebung reagiert. Das intelligente Gerät kann die Verarbeitung auch vom Master abkoppeln, indem es eine Inline-Analyse, benutzerdefinierte Triggerung und Signalbearbeitung am Knoten durchführt. Die Verwendung von LabVIEW FPGA ebnet außerdem den Weg für Domänenexperten, ihre Ideen schnell zu prototypisieren und umzusetzen, ohne VHDL-Programmierer zu sein.

Unterschiede in der API für die LabVIEW FPGA-Programmierung

Wenn Sie mit der Programmierung in LabVIEW FPGA für CompactRIO und anderen rekonfigurierbaren I/O-Plattformen von NI vertraut sind, gibt es einige Unterschiede zwischen dem lokalen FPGA und dem FPGA für EtherCAT RIO. In LabVIEW 2009 hat NI benutzerdefinierte I/O-Variablen eingeführt, um die FPGA-Daten des Slave-Geräts mit der Echtzeitverarbeitung des Masters zu synchronisieren. Diese benutzerdefinierten I/O-Variablen sind auch das einzige Mittel zur Datenübertragung zwischen dem Echtzeitprogramm des Controllers und dem FPGA-Programm des Erweiterungs-Chassis.

Tabelle 1: Vergleichen Sie FPGA-Übertragungsmethoden für lokale Chassis mit Erweiterungs-Chassis.

Nach dem Hinzufügen des FPGA-Zielsystems zum EtherCAT RIO-Slave im LabVIEW-Projektfenster können Sie eine benutzerdefinierte I/O-Variable erstellen, indem Sie mit der rechten Maustaste auf das EtherCAT RIO-Gerät klicken und „Hinzufügen»Benutzerdefinierte Variable“ auswählen. Variablenname, Datentyp und Datenrichtung (vom Host zum FPGA oder umgekehrt) können im Fenster „Eigenschaften“ festgelegt werden. Es ist wichtig zu beachten, dass die Anzahl der benutzerdefinierten I/O-Variablen, die Sie im FPGA-Modus des Slaves erstellen können, begrenzt ist. Das EtherCAT RIO kann insgesamt 512 Byte Eingangsdaten und 512 Byte Ausgangsdaten für I/O-Variablen im Scan-Modus und benutzerdefinierte I/O-Variablen im FPGA-Modus aufnehmen. Wenn Sie beispielsweise vier 32-Kanal-Module im Scan-Modus verwenden und jeder Kanal 32 Bit Daten aufnimmt, verwenden I/O-Variablen im Scan-Modus 256 Byte Eingangsdaten. Mit den verbleibenden 256 Byte Eingangsdaten können Sie bis zu 64 benutzerdefinierte I/O-Eingangsvariablen (ebenfalls 32 Bit Länge) im FPGA-Modus erstellen.

Abbildung 2: Sie können benutzerdefinierte I/O-Variablen erstellen, um zwischen dem Echtzeitcode des Masters und dem FPGA-Code des Slaves zu kommunizieren.

Spezielle FPGA-Funktionen und Anwendungsfälle

Diese benutzerdefinierten I/O-Variablen übertragen bei jedem Scan-Zyklus Einzelwertdaten an den Master-Controller und eignen sich daher am besten für das Weiterleiten verarbeiteter Daten vom EtherCAT RIO-Erweiterungs-Chassis. In einer NIWeek 2009-Keynote nutzten Moderatoren beispielsweise sechs EtherCAT RIO-Slave-Chassis, um mehrere musikalische Glockenspiele zu läuten, die ein Lied abspielten. Der Echtzeitcode des Masters steuerte das Timing, wann jedes verteilte Glockenspiel ausgelöst werden sollte, aber der FPGA auf dem Slave-Chassis zeichnete die Audiosignalverlaufsmessungen von einem Mikrofon auf und führte eine schnelle Fourier-Transformation (FFT) durch, um die Schallintensität für eine bestimmte Glockenspielfrequenz zu ermitteln. Das Slave-FPGA nutzte dann die Pulsweitenmodulation (PWM), um die Helligkeit einer Reihe von LEDs entsprechend der Lautstärke des Glockenspiels zu steuern. Auch ohne das laufende Echtzeitprogramm würden diese LEDs aufgrund der FPGA-Logik im EtherCAT RIO-Erweiterungs-Chassis bei denselben Glockenspielfrequenzen auch auf andere laute Geräusche reagieren.

Abbildung 3. Dieser EtherCAT RIO-FPGA-Code wurde in einer NIWeek 2009-Keynote-Demo verwendet, um mehrere musikalische Glockenspiele zu läuten, die ein Lied gespielt haben.

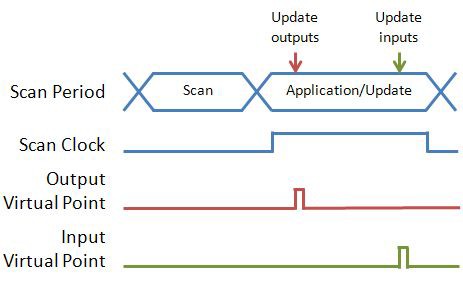

Zusätzlich zu den Funktionen des LabVIEW FPGA-Algorithmus bietet das Slave-Chassis verschiedene Chassis-I/O-Signale, um Ihren Programmcode anzupassen und zu synchronisieren. Mit EtherCAT State können Sie beispielsweise bestimmte FPGA-Logik während eines der sieben EtherCAT-Zustände ausführen. Wenn daher die Kommunikation mit dem Master-Controller beendet wird, geht das EtherCAT RIO-Erweiterungs-Chassis in den sicheren Betriebszustand über und der FPGA-Code kann das entsprechende sichere Verhalten festlegen. Ein weiteres nützliches Signal ist der virtuelle Ausgangs- und Eingangspunkt. Diese beiden Timing-Signale zeigen genau an, wann jeder Slave während jeder Scan-Periode seine Ausgangs- und Eingangswerte aktualisiert. Ihre steigenden Flanken können daher zur Synchronisation von FPGA-Code auf mehreren EtherCAT RIO-Erweiterungs-Chassis verwendet werden. Der NI-Industrial Communications for EtherCAT-Treiber enthält LabVIEW-Beispiele, um verschiedene fortgeschrittene FPGA-Funktionen wie die Synchronisation mit der NI Scan Engine, digitale Spezialsignale und asynchrones Oversampling zu demonstrieren.

Abbildung 4. Synchronisieren Sie Ihren EtherCAT-I/O-FPGA-Code mit virtuellen Timing-Signalen.

Zusammenfassung

Durch die Verwendung deterministischer verteilter I/O wie dem EtherCAT RIO-Erweiterungs-Chassis wird sichergestellt, dass Sie das für Echtzeitanwendungen erforderliche enge Timing und die Synchronisation beibehalten können. Durch das Hinzufügen von Hardware-FPGA-Code zu EtherCAT RIO-Slaves können Sie die Verarbeitung vom Controller abkoppeln und die Reaktionszeit durch intelligente Entscheidungen am Knoten verkürzen.