# **'Direct RF to Bits' Testing**

Introducing the Digital Signal Transceiver (DST)

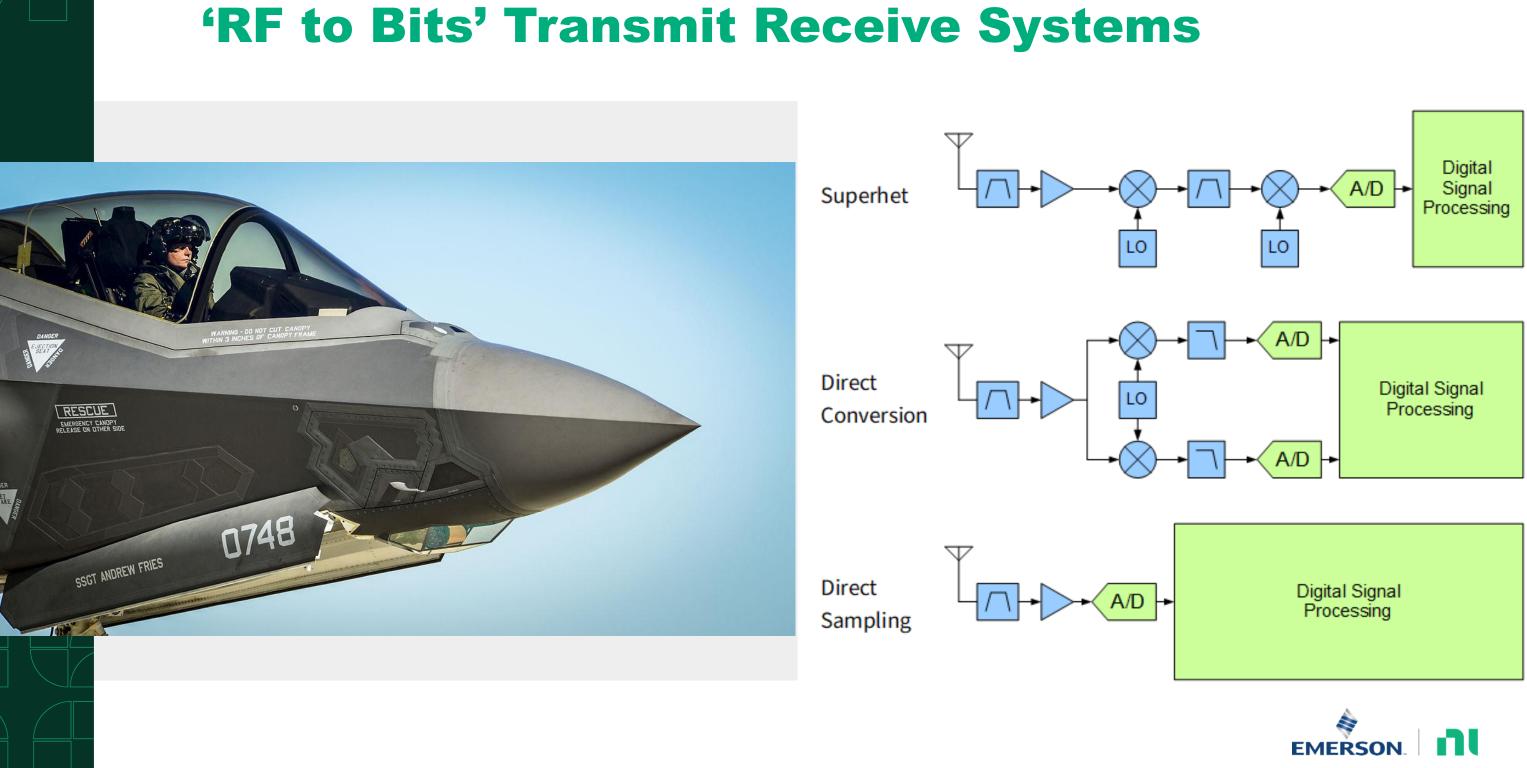

# **Define 'RF to Bits' Devices**

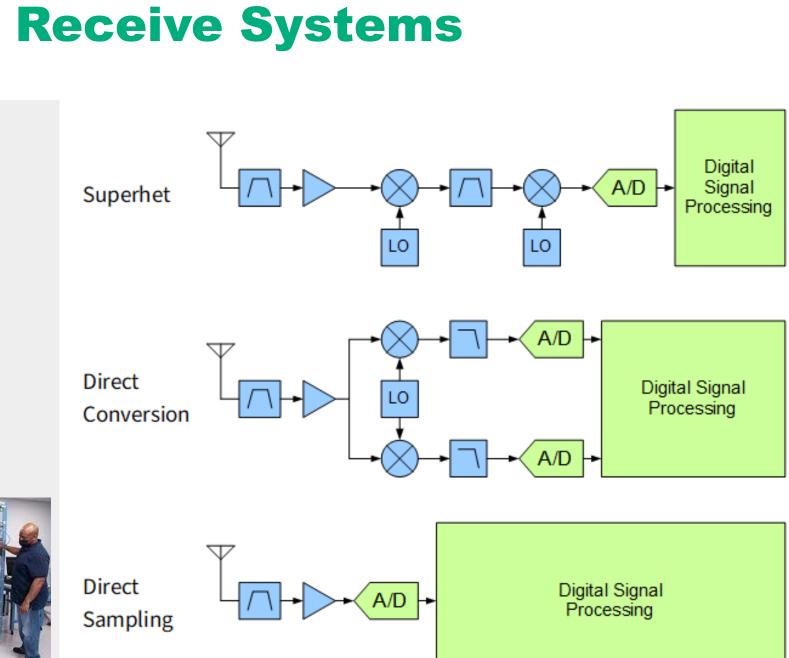

### RFSoC Enabled Devices Capable of Direct Sampling Wide-Band RF Signals

- Commonly sampling above 6GSa/sec to rates >64GSa/sec

- Significantly decreases component count to perform common operations like beamforming

- Digitally up/down converts signals and performs basic processing (gain, phase, eq)

- Requires digital bandwidths up to and beyond 100Gb/sec

- Flexible onboard FPGA with MGT streams to secondary processor

- Breaks common RF paradigm for using a VNA to test everything

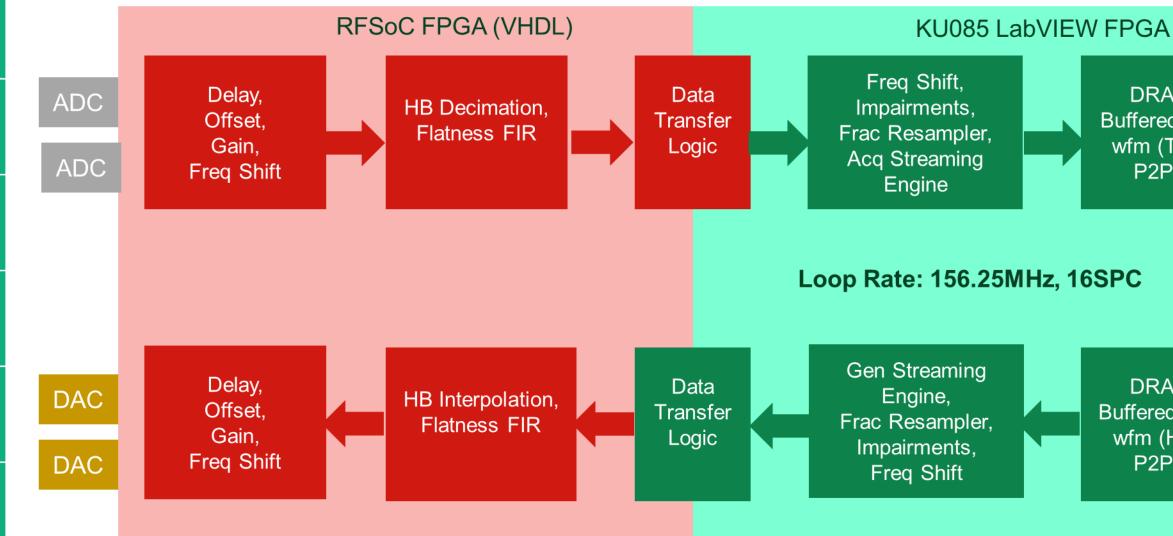

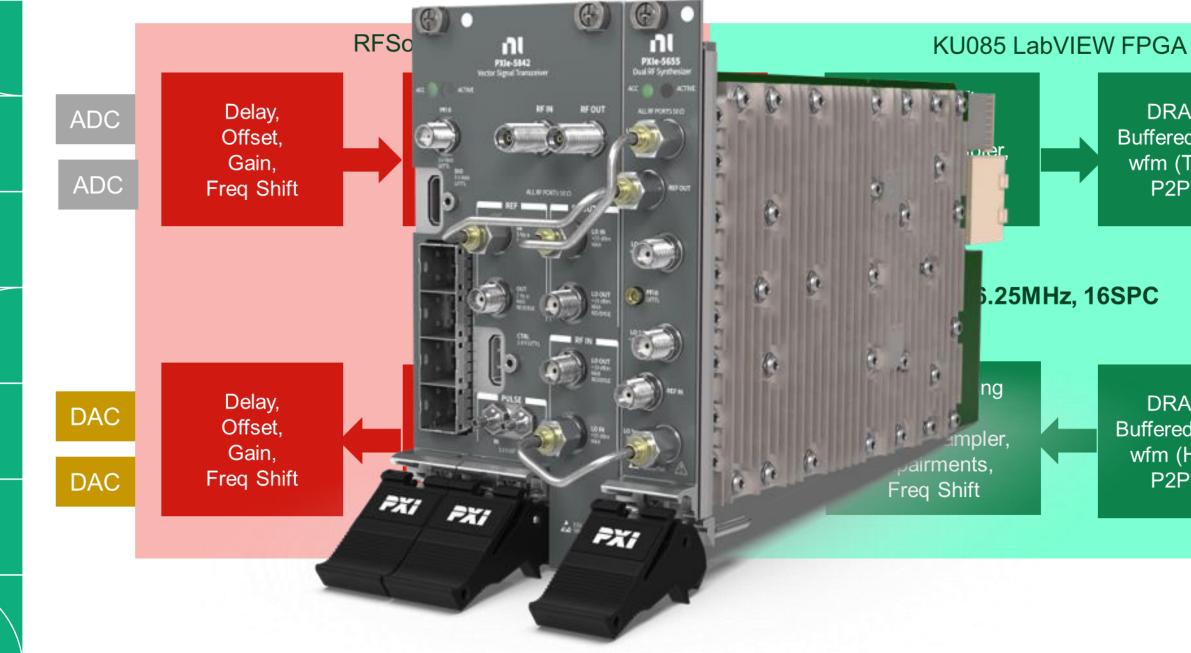

# PXIe-5842 VST – 5GSa/s 'RFSoC' Device

DRAM **Buffered Acq** wfm (T2H, P2P\*)

DRAM Buffered Gen wfm (H2T, P2P\*)

# PXIe-5842 VST – 5GSa/s 'RFSoC' Device

DRAM Buffered Acq wfm (T2H, P2P\*)

DRAM Buffered Gen wfm (H2T, P2P\*)

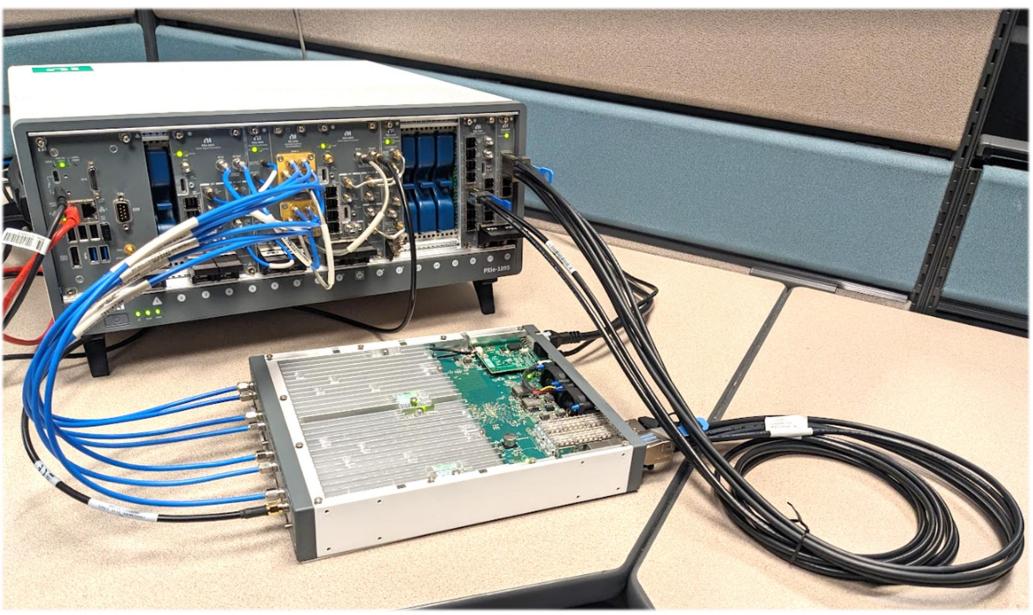

# **Application: 'RF to Bits' Transmit Receive Systems**

Human for Scale

# **Application:**

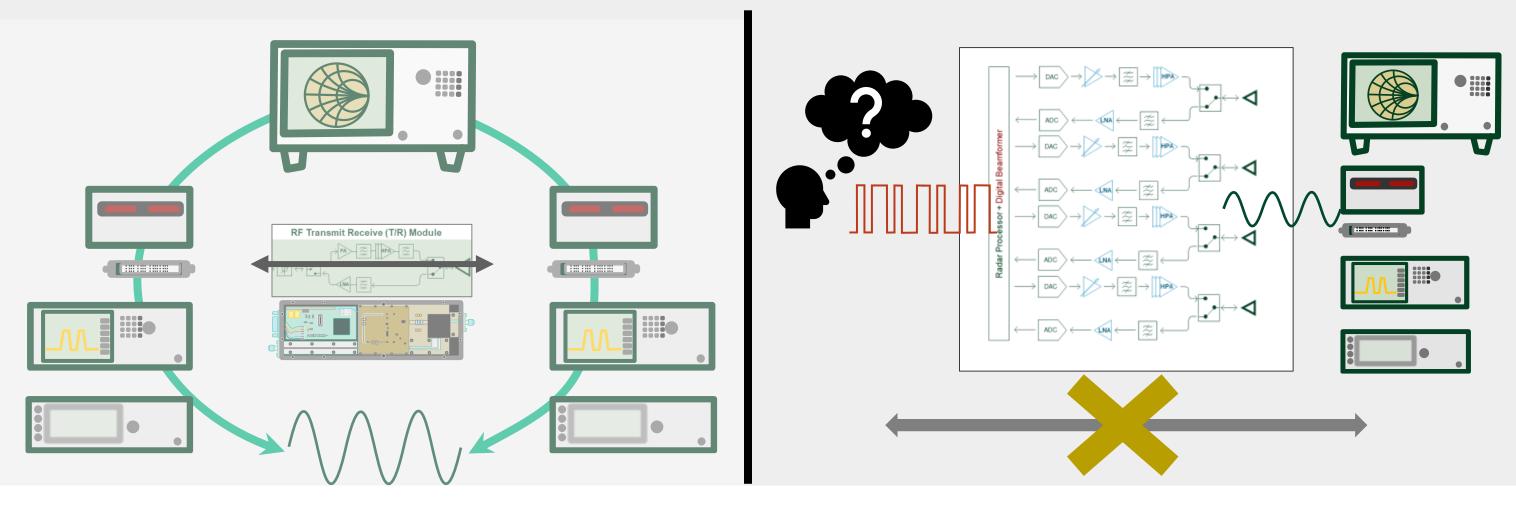

# **Industry Situation**

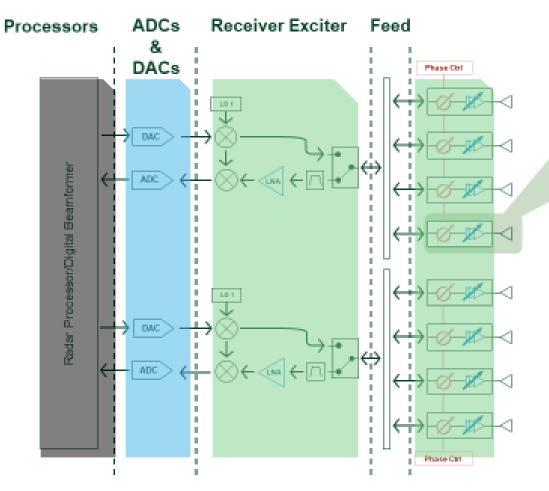

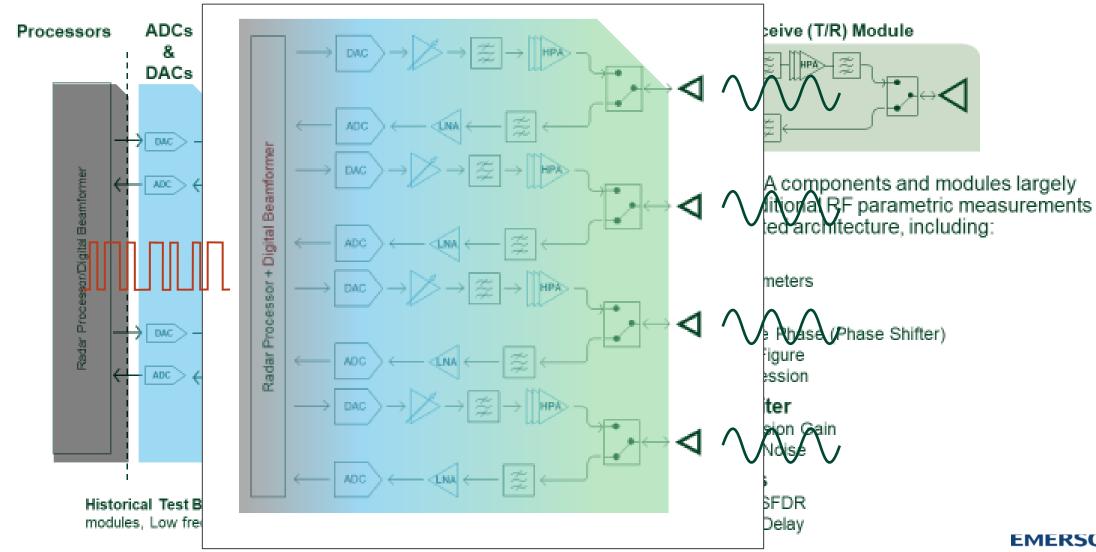

Active Electronically Scanned Array (AESA) antenna systems & signal chains have evolved from multiple, discretely testable, analog modules into digitally dominated transceiver systems with directly integrated high speed converters (ADC/DAC).

Historical Test Boundaries Maintained - RF components and modules, Low frequency Data Converters, and Digital Processors

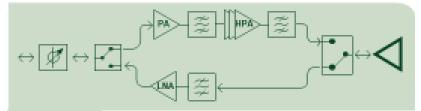

#### RF Transmit Receive (T/R) Module

Testing of AESA components and modules largely consists of traditional RF parametric measurements due to distributed architecture, including:

#### Common:

S-Parameters

#### T/R Modules

- Relative Phase (Phase Shifter)

- Noise Figure

- Compression

#### Receiver/Exciter

- Conversion Gain

- Phase Noise

#### ADCs & DACs

- SNR / SFDR

- Group Delay

# **Industry Situation**

Active Electronically Scanned Array (AESA) antenna systems & signal chains have evolved from multiple, discretely testable, analog modules into digitally dominated transceiver systems with directly integrated high speed converters (ADC/DAC).

# **Industry Challenge**

Traditional AESA measurement methodologies and instruments, commonly utilizing analog VNAs, are incapable of fully addressing the modern signal & demands of these newly digitally integrated transceiver modules (DTRM).

# **Problem Breakdown**

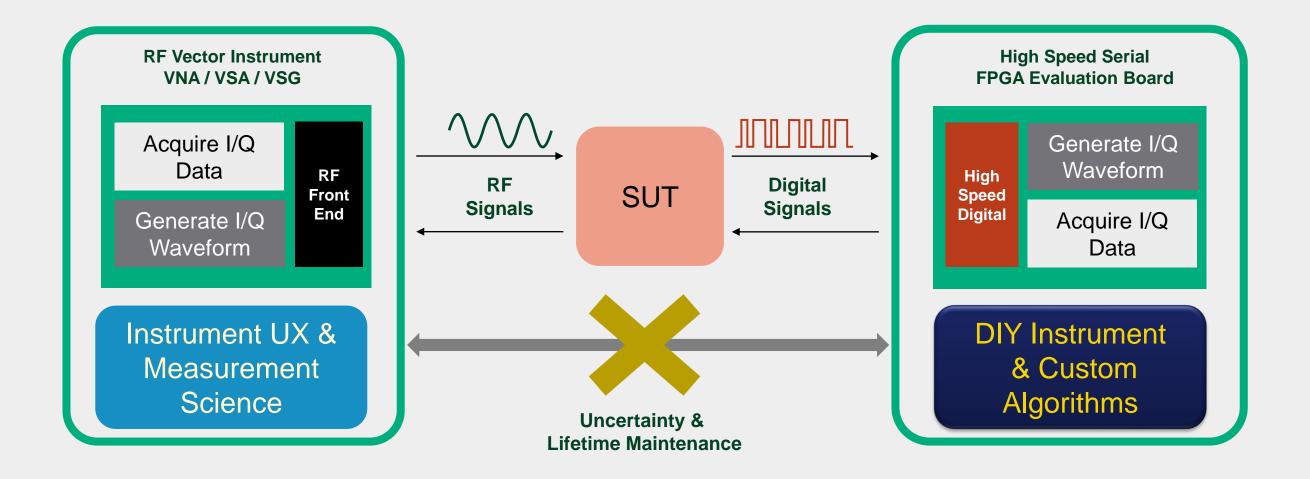

#### Digital Connectivity Not Ready To Scale

### **Underperforming Measurement Science**

# What Connects to Your Digital?

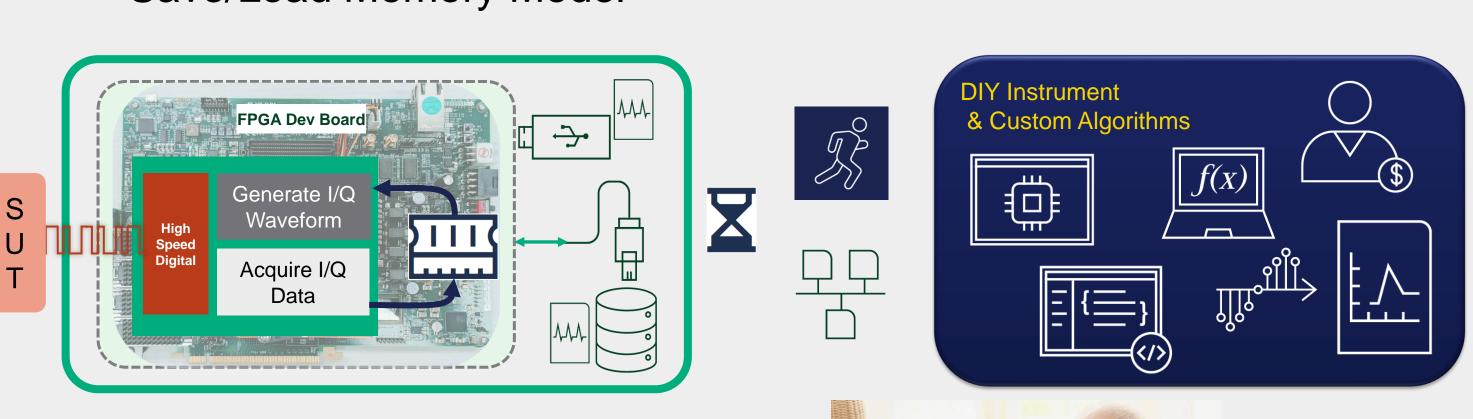

### Evaluation / Home-Grown 'Solutions'

- Test departments <u>not equipped</u> with High-Speed-Serial (HSS) interfaces

- Home-grown digital solutions <u>costly</u> and difficult to produce at scale, maintain and deploy over a program's lifecycle

- Evaluation boards not designed or manufactured to be <u>long</u> term scalable solutions

- Memory and data transfer size and rates <u>limit test time</u>

<u>performance</u>

- Not suited for production or your SUT connectivity demands

### Functional but Not Practical at Production

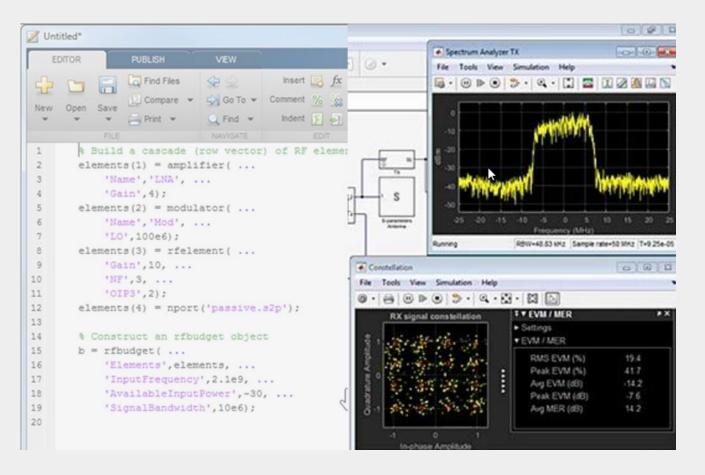

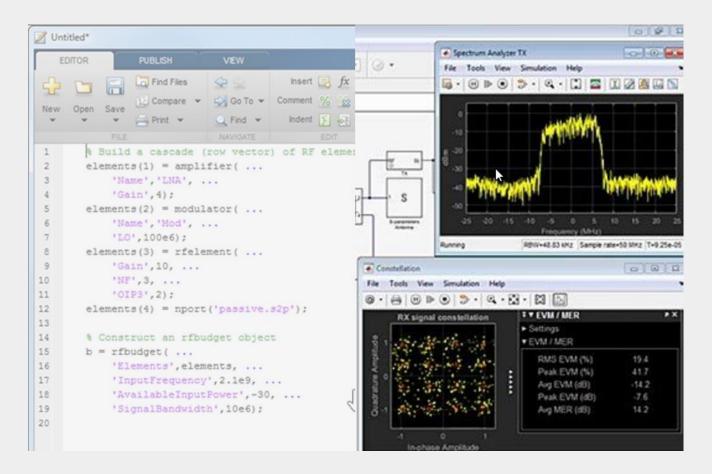

# **How Do You Calibrate and Correlate?**

### Slow Results on Custom Algorithms

# Spend time measuring your device and not developing Instrumentation IP

- Moving large data around memory or files is inherently slow

- Developing algorithms that display a result are easy, getting to good results you to correlate is hard

- Stimulus response measurements should have instrumentation on both stimulus and response

- Most custom algorithms and API are not developed for scalability, long term maintenance or speed

- Complex measurements like pulse profile analysis should be <u>common regardless of domain (analog or digital)</u>

# **RF to Digital Workflows**

# **RF to Digital Workflows**

Save/Load Memory Model

# **DIY Digital Instrument Model**

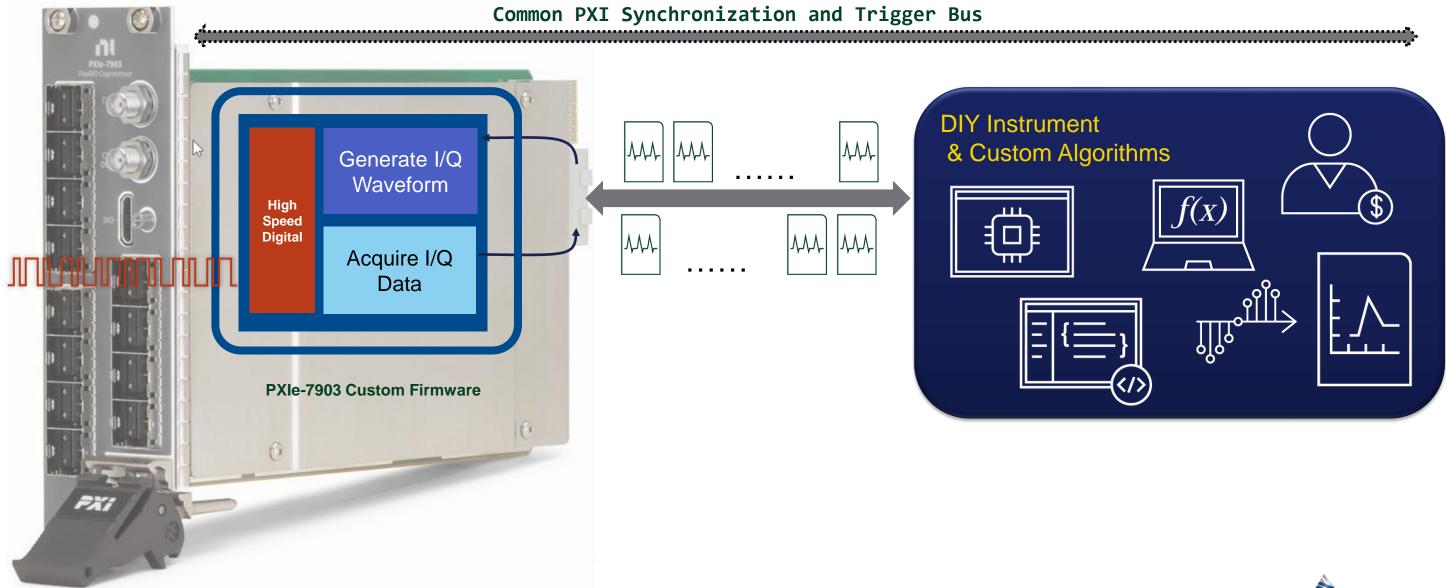

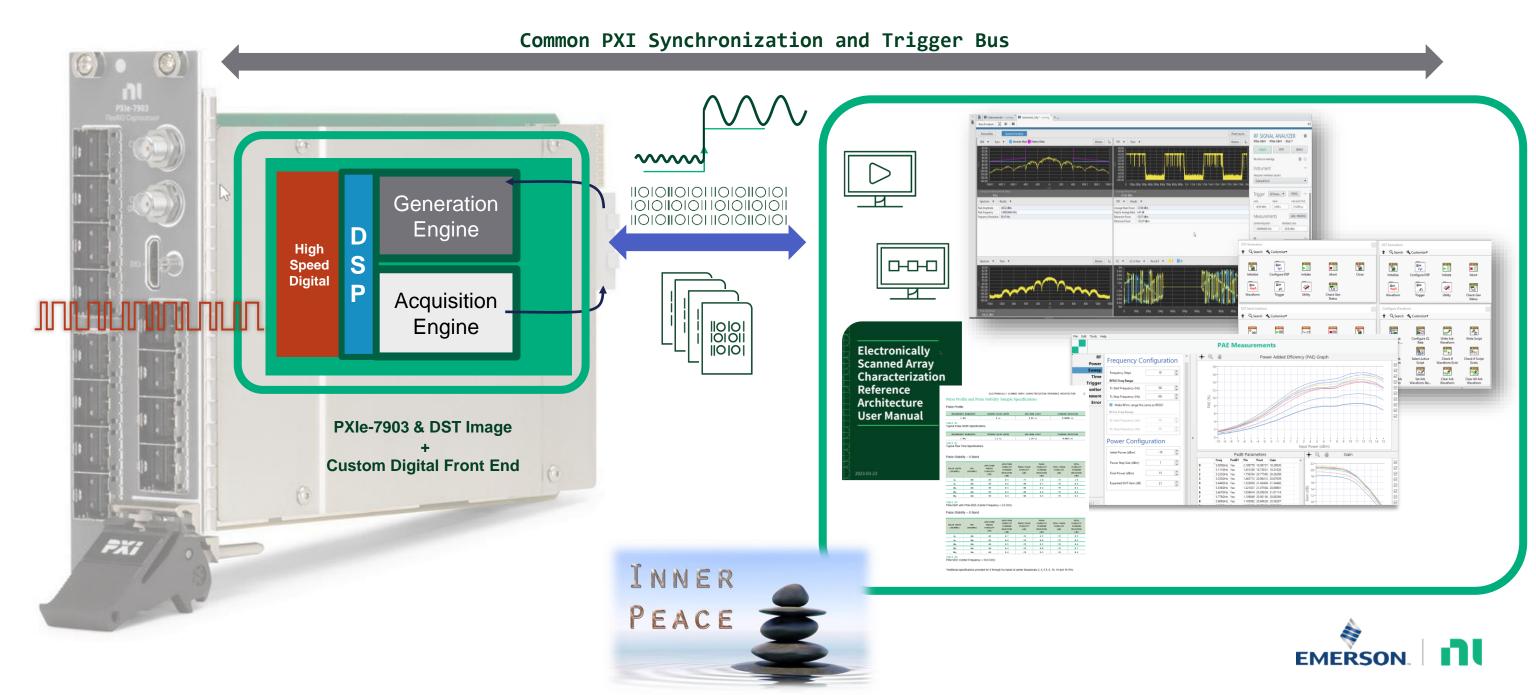

# **DST - Digital Signal Transceiver**

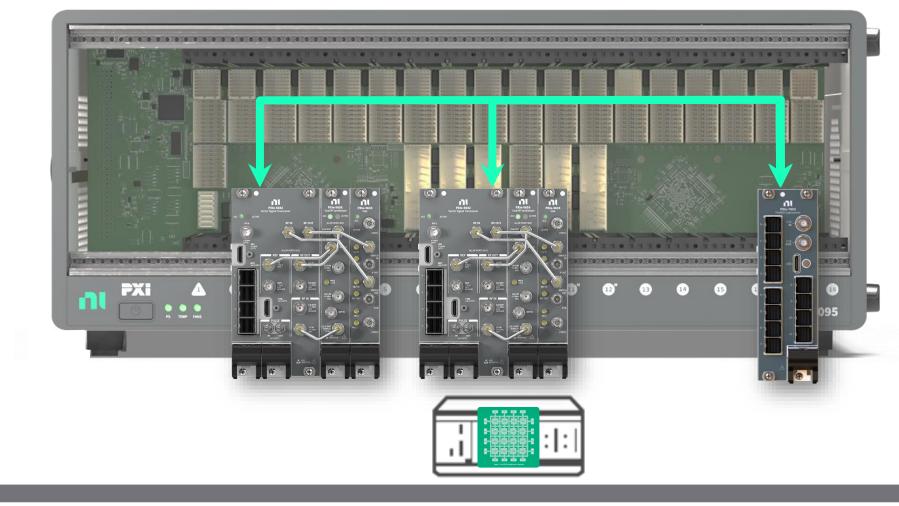

# **Re-establishing the Instrumentation Hug**

Common PXI Synchronization and Trigger Bus

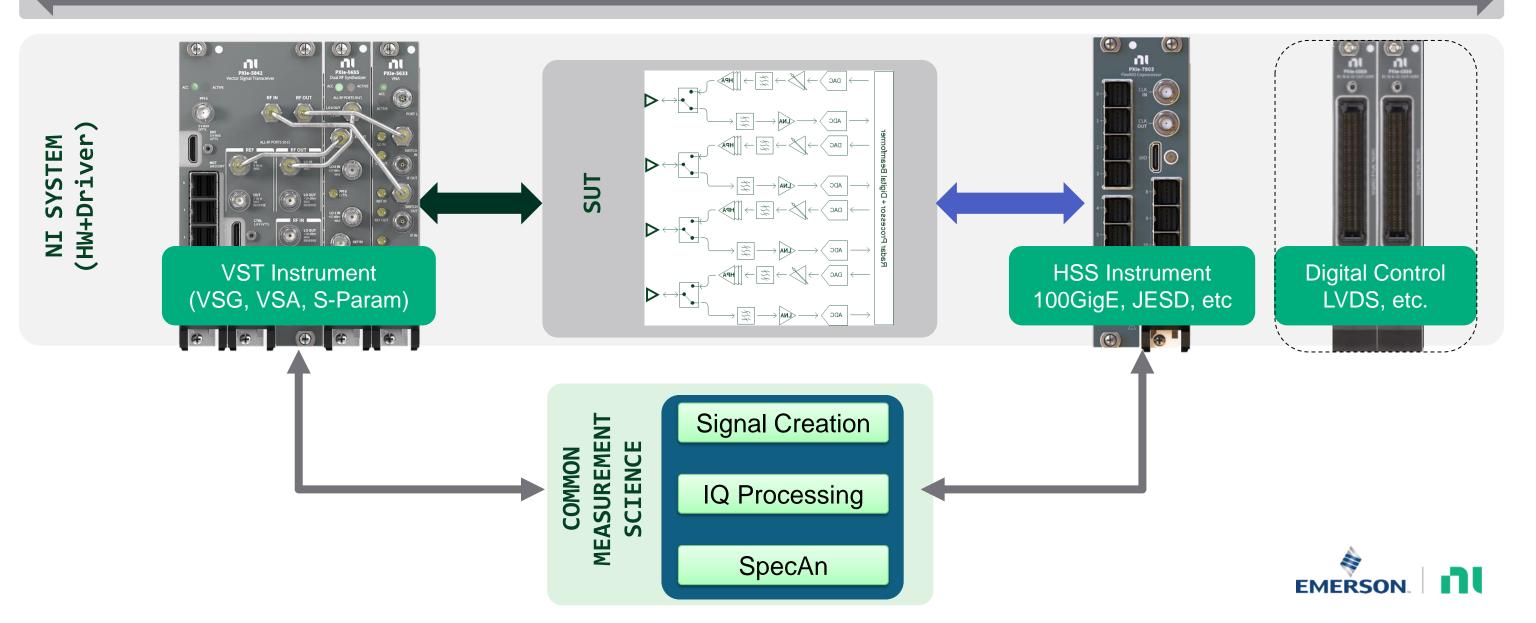

# **Instrument Coordination View**

Common PXI Synchronization and Trigger Bus

# **System Under Test**

# **Preview Demo**

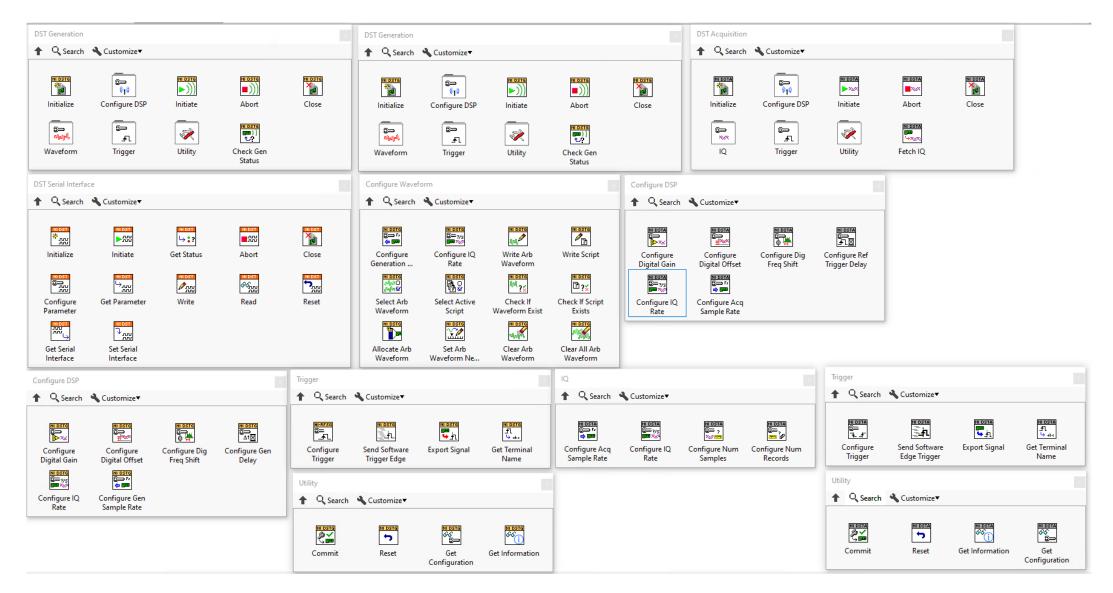

# **DST Instrument** Workflow

Design and Development **Accelerators**

- Interactive out of the box

- No-code acquisition and visualization

- Debug platform for designers

- Extensible interface through Instrument Studio \_

- Instrument Grade Automation API

- Features and interfaces mirrored from RFSA/G

- Powerful trigger engines

- Waveform scripting

- Stream data or capture records

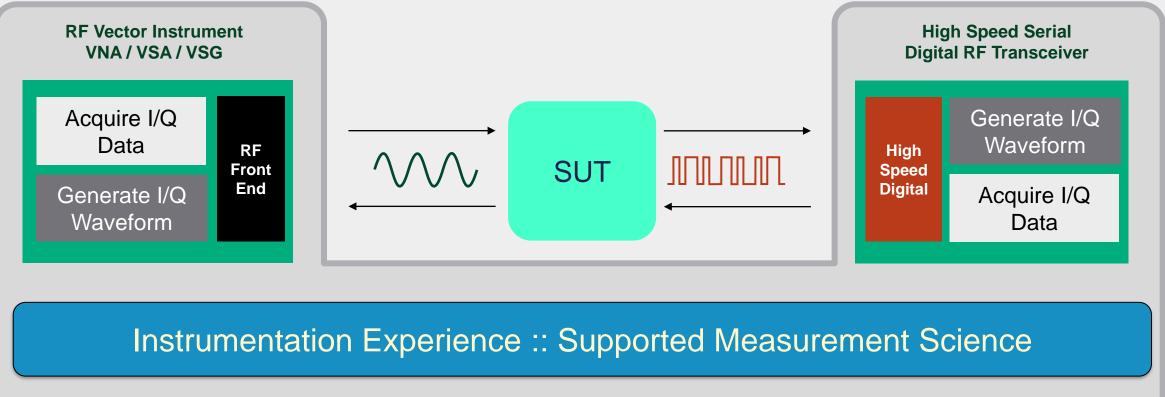

# **RF to Digital Workflows Digital RF Vector Instrument Model**

**Desired** Instrumentation – I/Q Stimulus and Response

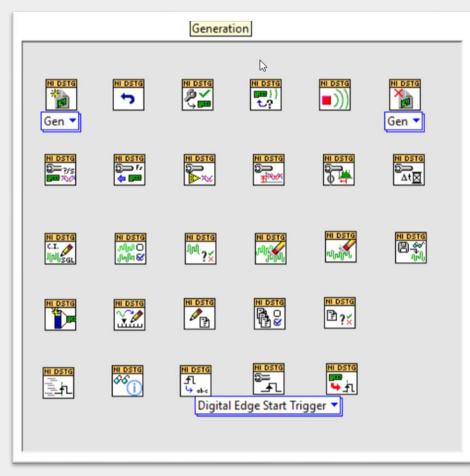

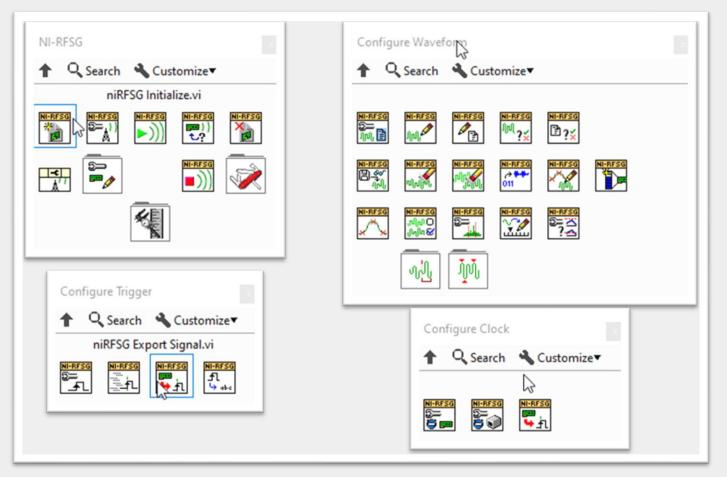

# **Instrument Grade API – Generation Comparison**

### DST-G

### NI-RFSG

# **Full Pallet Overview**

#### connact

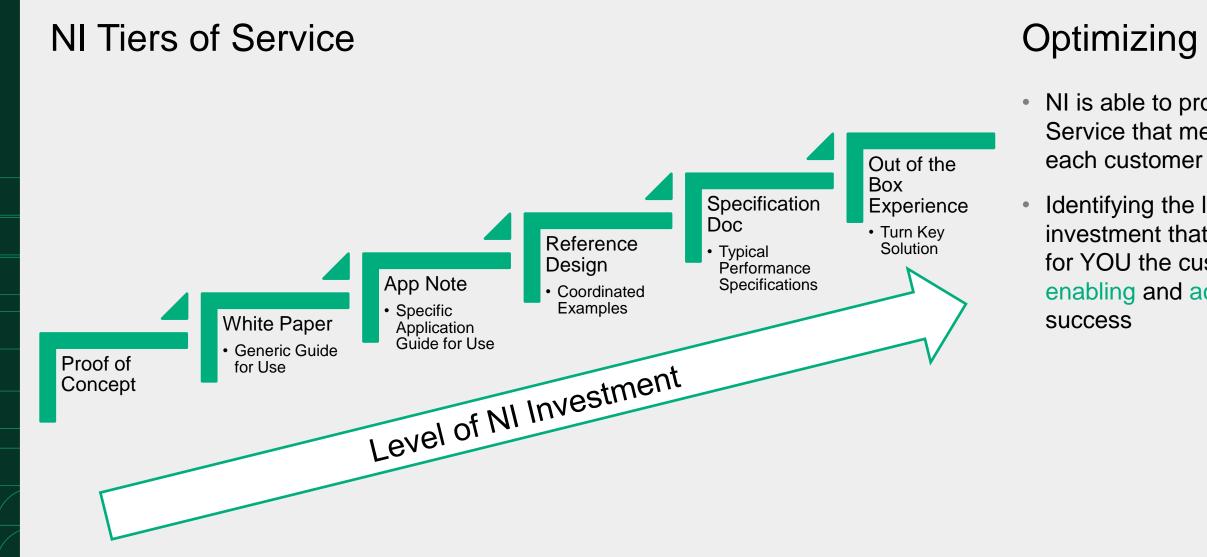

# **Easing the Struggle**

# **Optimizing Support**

• NI is able to provide Levels of Service that meet the needs of

Identifying the level of investment that is value added for YOU the customer is key to enabling and accelerating your

## **Norm Kirchner**

Offering Manager Norm.Kirchner@ni.com

# Kyle MacCoy

Solution Marketing Engineer Kyle.MacCoy@ni.com